# Embedded Target for the TI TMS320C2000™ DSP Platform

For Use with Real-Time Workshop®

- Modeling

- Simulation

- Implementation

#### How to Contact The MathWorks:

www.mathworks.com comp.soft-sys.matlab

Newsgroup

Web

www.mathworks.com/contact TS.html Technical Support

suggest@mathworks.com bugs@mathworks.com doc@mathworks.com service@mathworks.com info@mathworks.com

Product enhancement suggestions Bug reports

Documentation error reports

Order status, license renewals, passcodes Sales, pricing, and general information

508-647-7000 (Phone)

508-647-7001 (Fax)

The MathWorks, Inc. 3 Apple Hill Drive Natick, MA 01760-2098

For contact information about worldwide offices, see the MathWorks Web site.

Embedded Target for the TI TMS320C2000™ DSP Platform User's Guide © COPYRIGHT 2003–2006 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### **Trademarks**

MATLAB, Simulink, Stateflow, Handle Graphics, Real-Time Workshop, and xPC TargetBox are registered trademarks of The MathWorks, Inc.

Other product or brand names are trademarks or registered trademarks of their respective holders.

#### **Patents**

The MathWorks products are protected by one or more U.S. patents. Please see www.mathworks.com/patents for more information.

#### **Revision History**

| November 2003  | Online only | New for Version 1.0 (Release 13SP1+)      |

|----------------|-------------|-------------------------------------------|

| June 2003      | Online only | New for Version 1.1 (Release 14)          |

| October 2004   | Online only | Revised for Version 1.1.1 (Release 14SP1) |

| December 2004  | Online only | Revised for Version 1.2 (Release 14SP1+)  |

| March 2005     | Online only | Revised for Version 1.2.1 (Release 14SP2) |

| September 2005 | Online only | Revised for Version 1.3 (Release 14SP3)   |

| March 2006     | Online only | Revised for Version 2.0 (Release 2006a)   |

# Contents

# **Getting Started**

|   |   | , |

|---|---|---|

| , | 1 | ı |

|   |   | • |

|   |   | ı |

|   |   |   |

| What Is the Embedded Target for the TI TMS320C2000 |            |

|----------------------------------------------------|------------|

| DSP Platform? Suitable Applications                | 1-2<br>1-2 |

| Setting Up and Configuring                         | 1-3        |

| System Hardware and Operating                      | 1-3        |

| Supported Hardware for Targets                     | 1-3        |

| Software Requirements                              | 1-5        |

| Verifying the Configuration                        | 1-7        |

| Embedded Target for TI C2000 and Code Composer     |            |

| Studio                                             | 1-9        |

| Default Project Configuration                      | 1-9        |

| Data Type Support                                  | 1-10       |

| Scheduling and Timing                              | 1-11       |

| Timer-Based Interrupt Processing                   | 1-11       |

| Asynchronous Interrupt Processing                  | 1-13       |

| Overview of Creating Models for Targeting          | 1-15       |

| Online Help                                        | 1-15       |

| Blocks to Avoid Using in Your Models               | 1-16       |

| S-Function Builder Blocks                          | 1-17       |

| Setting Simulation Configuration Parameters        | 1-17       |

| Building Your Model                                | 1-18       |

| Using the c2000lib Blockset                        | 1-20       |

| Hardware Setup                                     | 1-20       |

| Starting the c2000lib Library                      | 1-20       |

| Setting Up the Model                               | 1-22       |

| Adding Blocks to the Model                         | 1-28       |

| Generating Code from the Model                                 | 1-31              |

|----------------------------------------------------------------|-------------------|

| Loading                                                        | 1-32              |

| Using the IQmath Libi                                          | rary              |

|                                                                |                   |

| About the IQmath Library                                       | 2-2<br>2-2        |

| Fixed-Point Numbers Signed Fixed-Point Numbers                 | 2-4<br>2-4        |

| Q Format Notation                                              | 2-5               |

| Building Models  Converting Data Types Using Sources and Sinks | 2-9<br>2-9<br>2-9 |

| Choosing Blocks to Optimize Code                               | 2-9               |

| Blocks — By Categ                                              | gory              |

| C2000 Target Preferences Library (c2000tgtpreflib)             | 3-2               |

| Host-side CAN Blocks (c2000canlib)                             | 3-3               |

| C2000 RTDX Instrumentation Library (rtdxBlocks)                | 3-4               |

| C2400 DSP Chip Support Library (c2400dspchiplib)               | 3-5               |

| C280x DSP Chip Support Library (c280xdspchiplib)               | 3-6               |

| C281x DSP Chip Support Library (c281xdspchiplib)               | 3-7               |

|            | C28x Digital Motor Control Library (c28xdmclib) | 3-9  |

|------------|-------------------------------------------------|------|

|            | C28x IQmath Library (tiiqmathlib)               | 3-10 |

| <b>4</b> [ | Blocks — Alphabetical                           | List |

| <b>T</b>   | In                                              | dex  |

| Γ          |                                                 | uca  |

# Getting Started

This chapter describes how to use the Embedded Target for TI C2000<sup>TM</sup> DSP to create and execute applications on Texas Instruments C2000 development boards. To use the targeting software, you should be familiar with using Simulink® to create models and with the basic concepts of Real-Time Workshop® automatic code generation. To read more about Real-Time Workshop, refer to the Real-Time Workshop documentation.

What Is the Embedded Target for the TI TMS320C2000 DSP Platform? (p. 1-2)

Introduces the Embedded Target for TI C2000 DSP and describes some of its features and supported hardware

Setting Up and Configuring (p. 1-3)

Describes the software and hardware required to use the Embedded Target for the TI TMS320C2000 DSP Platform and how to set them up

Embedded Target for TI C2000 and Code Composer Studio (p. 1-9)

Provides information about Code Composer Studio™

Data Type Support (p. 1-10)

Compares the data types supported by Simulink and the TI C2000 DSP chips

Scheduling and Timing (p. 1-11)

Provides information about TI C2000 scheduling

Overview of Creating Models for Targeting (p. 1-15)

Summarizes the steps required to create models for your target

Using the c2000lib Blockset (p. 1-20)

Provides an example of creating a model and targeting hardware

# What Is the Embedded Target for the TI TMS320C2000 DSP Platform?

The Embedded Target for the TI TMS320C2000<sup>TM</sup> DSP Platform integrates Simulink® and MATLAB® with Texas Instruments eXpressDSP<sup>TM</sup> tools. You can use this product to develop and validate digital signal processing and control designs from concept through code.

The Embedded Target for the TI TMS320C2000 DSP Platform uses C code generated by Real-Time Workshop® and your TI development tools to generate a C language real-time implementation of your Simulink model. Real-Time Workshop builds a Code Composer Studio™ project from the C code.

You can compile, link, download, and execute the generated code on an LF2407, F2808, or F2812 eZdsp™ DSP board from Spectrum Digital, Inc. or on a custom board based on a TI C280x or C281x chip.

# **Suitable Applications**

The Embedded Target for the TI TMS320C2000 DSP Platform enables you to develop digital signal processing and control applications. Some important characteristics of the applications that you can develop are

- Asynchronous scheduling

- Flash-based standalone applications

- Fixed-point arithmetic

- Single rate

- Multirate

- Adaptive

- Frame based

# **Setting Up and Configuring**

# Platform Requirements — Hardware and Operating System

To run the Embedded Target for the TI TMS320C2000 DSP Platform, your host PC must meet the following hardware configuration requirements:

- Intel Pentium or Intel Pentium processor-compatible PC

- 64 MB RAM (128 MB recommended)

- 20 MB hard disk space available after installing MATLAB

- Color monitor

- One parallel printer port or one USB port to connect your target board to your PC

- CD-ROM drive

- Windows 2000 or Windows XP

You may need additional hardware, such as signal sources and generators, oscilloscopes or signal display systems, and assorted cables to test and evaluate your application on your hardware.

## **Supported Hardware for Targets**

The Embedded Target for TI C2000 DSP supports the following boards:

- DSP Starter Kits (DSKs) from Spectrum Digital, Inc.

- $\blacksquare$  TMS320F2812 eZdsp DSK the F2812eZdsp DSP Starter Kit

- $\blacksquare$  TMS320F2808 eZdsp DSK the F2808eZdsp DSP Starter Kit

- $\blacksquare$  TMS320LF2407 eZdsp DSK the LF2407eZdsp DSP Starter Kit

The above DSKs help developers evaluate digital signal processing applications for the Texas Instruments DSP chips. You can create, test, and deploy your processing software and algorithms on the target processor without the difficulties inherent in starting with the digital signal processor itself and building the support hardware to test the application on the

processor. Instead, the development board provides the input hardware, output hardware, timing circuitry, memory, and power for the digital signal processor. Texas Instruments provides the software tools, such as the C compiler, linker, assembler, and integrated development environment, for PC users to develop, download, and test their algorithms and applications on the processor.

Refer to the documentation provided with your hardware for information on setting up and testing your target board.

**Note** To generate code, and download the code to your target board, you do not need to change any jumpers from their factory defaults on either the LF2407 or F2812 target board.

However, if you want to run your code from flash memory on the F2808 or F2812, you do need to change settings on the board. For more information on this, see "Running Code from Flash Memory" on page 1-5.

**Note** In factory default condition, both the LF2407 and F2812 target boards are set to operate in microcontroller mode. The Embedded Target for the TI TMS320C2000 DSP Platform does not support microprocessor mode.

- Custom boards based on any of the following Texas Instruments C2000 Digital Signal Controllers:

- TMS320F2801

- TMS320F2806

- TMS320F2808

- **-** TMS320C2810

- TMS320F2810

- TMS320C2811

- TMS320F2811

- TMS320R2811

- TMS320C2812

- TMS320F2812

- TMS320R2812

#### **Running Code from Flash Memory**

Running code from flash memory is supported on both the F2808 and F2812 eZdsp DSKs. Although you can generate and download code to the F2808 or F2812 eZdsp DSK with the board in factory default condition, you need to change hardware settings on the board before you can run code from flash memory.

For the F2812, you need to change the jumper settings from their factory defaults. For more information on this, see the discussion of the jumper settings for Boot Mode in the  $eZdsp^{TM}$  F2812 Technical Reference, available from the Spectrum Digital Web site at http://c2000.spectrumdigital.com/ezf2812/.

For the F2808, you need to change DIP switch settings. For more information on this, see the  $eZdsp^{TM}$  F2808 USB Technical Reference, available from the Spectrum Digital Web site at http://c2000.spectrumdigital.com/ezf2808/.

# **Software Requirements**

#### MathWorks Software

For information about other MathWorks software required to use the Embedded Target for the TI TMS320C2000 DSP Platform, refer to the MathWorks Web site — http://www.mathworks.com. Check the Products area for the Embedded Target for the TI TMS320C2000 DSP Platform.

For information about the software required to use the Link for Code Composer Studio Development Tools, refer to the Products area of the MathWorks Web site — http://www.mathworks.com.

#### **Texas Instruments Software**

In addition to the required software from The MathWorks, Embedded Target for the TI TMS320C2000 DSP Platform requires that you install the Texas Instruments development tools and software listed in the following table. Installing Code Composer Studio IDE Version 3.1 for the C2000 series installs the software shown.

#### Required TI Software for Targeting Your TI C2000 Hardware

| Installed<br>Product                   | Additional Information                                                                                                                                                                                    |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Assembler                              | Creates object code (.obj) for C2000 boards from assembly code                                                                                                                                            |

| Compiler                               | Compiles C code from the blocks in Simulink models into object code (.obj). As a by-product of the compilation process, you get assembly code (.asm) as well.                                             |

| Linker                                 | Combines various input files, such as object files and libraries                                                                                                                                          |

| Code Composer<br>Studio                | Texas Instruments integrated development environment (IDE) that provides code debugging and development tools                                                                                             |

| TI C2000<br>miscellaneous<br>utilities | Various tools for developing applications for the C2000 digital signal processor family                                                                                                                   |

| Code Composer<br>Setup Utility         | Program you use to configure your CCS installation by selecting your target boards or simulator                                                                                                           |

| Flash Plug-In                          | Plug-in you use in downloading generated code to flash memory. While this plug-in is not strictly required, it is very useful when working with flash memory. It is available through the CCS Web Update. |

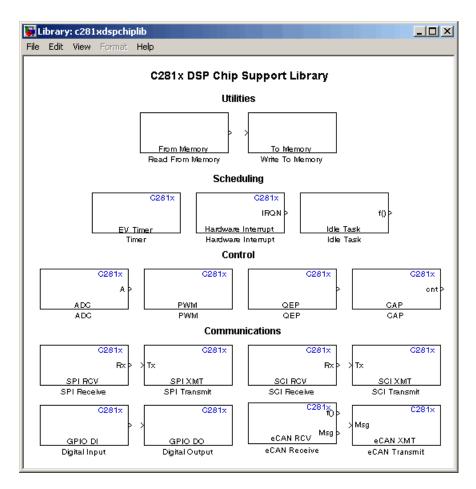

# **Verifying the Configuration**

To determine whether the Embedded Target for the TI TMS320C2000 DSP Platform is installed on your system, enter this command at the MATLAB prompt:

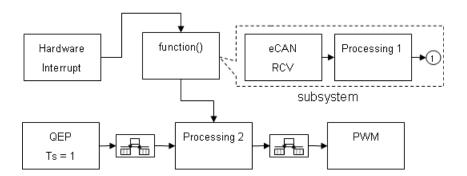

c2000lib

MATLAB displays the C2000 block library containing the following libraries and blocks that comprise the C2000 library:

- C2800 RTDX Instrumentation

- C2000 Target Preferences

- Host-side CAN Blocks

- C281x DSP Chip Support

- C280x DSP Chip Support

- C2400 DSP Chip Support

- C28x IQMath Library

- C28x DMC Library

- Info block

- Demos block

If you do not see the listed libraries, or MATLAB does not recognize the command, you need to install the Embedded Target for the TI TMS320C2000 DSP Platform. Without the software, you cannot use Simulink and Real-Time Workshop to develop applications targeted to the TI boards.

**Note** For information about system requirements, refer to the system requirements page, available in the Products area at the MathWorks Web site (http://www.mathworks.com).

To verify that Code Composer Studio (CCS) is installed on your machine, enter this command at the MATLAB prompt:

#### ccsboardinfo

With CCS installed and configured, MATLAB returns information about the boards that CCS recognizes on your machine, in a form similar to the following listing:

| Boar | d Board           | Proc Processor | Processor   |

|------|-------------------|----------------|-------------|

| Num  | Name              | Num Name       | Туре        |

|      |                   |                |             |

| 1    | F2812 Simulator   | 0 CPU          | TMS320C28xx |

| 0    | F2812 PP Emulator | 0 CPU 1        | TMS320C28xx |

If MATLAB does not return information about any boards, revisit your CCS installation and setup in your CCS documentation.

As a final test, launch CCS to ensure that it starts up successfully. For the Embedded Target for the TI TMS320C2000 DSP Platform to operate with CCS, the CCS IDE must be able to run on its own.

**Note** For any model to work in the targeting environment, you must select the discrete-time solver in the **Solver** pane of the Simulink Configuration Parameters dialog box. Targeting does not work with continuous-time solvers.

To select the discrete-time solver, from the main menu in your model window, select **Simulation > Configuration Parameters**. Then in the **Solver** pane, set the **Solver** option to discrete (no continuous states).

# **Embedded Target for TI C2000 and Code Composer Studio**

Texas Instruments (TI) facilitates development of software for TI DSPs by offering Code Composer Studio (CCS) Integrated Development Environment (IDE). Used in combination with your Embedded Target for TI C2000 DSP and Real-Time Workshop, CCS provides an integrated environment that, once installed, requires no coding.

Executing code generated from Real-Time Workshop on a particular target requires that Real-Time Workshop generate target code that is tailored to the specific hardware target. Target-specific code includes I/O device drivers and interrupt service routines (ISRs). Generated source code must be compiled and linked using CCS so that it can be loaded and executed on a TI DSP. To help you to build an executable, the Embedded Target for TI C2000 DSP uses the Link for Code Composer Studio to start the code building process within CCS. After you download your executable to your target and run it, the code runs wholly on the target. You can access the running process only from the CCS debugging tools or across a link using Link for Code Composer Studio Development Tools.

# **Default Project Configuration**

CCS offers two standard project configurations, Release and Debug. Project configurations define sets of project build options. When you specify the build options at the project level, the options apply to all files in your project. For more information about the build options, refer to your TI documentation. The models you build with the Embedded Target for TI C2000 DSP use a custom configuration that provides a third combination of build and optimization settings — custom\_MW.

#### Default Build Options in the custom\_MW Configuration

The default settings for custom\_MW are the same as the Release project configuration in CCS, except for the compiler options. custom\_MW uses Function(-o2) for the compiler optimization level.

Your CCS documentation provides complete details on the compiler build options. You can change the individual settings or the build configuration within CCS.

# **Data Type Support**

The TI C2000 DSP chips support 16-bit data types and do not have native 8-bit data types. Simulink and the Embedded Target for TI C2000 support many data types, including 8-bit data types.

If you select int8 or uint8 in your model, your simulation will run with 8-bit data, but in the generated code, that data will be represented as 16-bit. This may cause instances where data overflow and wraparound occurs in the simulation, but not in the generated code.

For example, if you want the overflow behavior of the simulation and generated code to match for a Simulink Add block in your model, select **Saturate on integer overflow** in that block.

# **Scheduling and Timing**

Normally the code generated by the Embedded Target for TI C2000 runs out of the context of a timer interrupt. Model blocks run in a periodical fashion clocked by the periodical interrupt whose period is tied to the base sample time of the model.

This execution scheduling model, however, is not flexible enough for many systems, especially control and communication systems, which must respond to external events in real time. Such systems require the ability to handle various hardware interrupts in an asynchronous fashion.

For C280x and C281x-based boards, Embedded Target for TI C2000 lets you model systems that include asynchronous hardware interrupt processing in addition to the tasks that are left to be handled in the context of the timer interrupt.

# **Timer-Based Interrupt Processing**

For code that runs in the context of the timer interrupt, each iteration of the model solver is run after an interrupt has been posted and serviced by an interrupt service routine (ISR). The code generated for the C280x or C281x uses CPU\_timer0. The code generated for the C24x uses an Event Manager (EV) timer, which you can select.

The timer is configured so that the model's base rate sample time corresponds to the interrupt rate. The timer period and prescaler are calculated and set up to ensure the desired rate as follows:

$$Base \ Rate \ Sample \ Time = \frac{Timer \ Period}{\binom{(Timer \ Clock \ Speed)}{Timer Clock Prescaler}}$$

The minimum achievable base rate sample time depends on the model complexity. The maximum value depends on the maximum timer period value (2<sup>32</sup>-1 for the F2812 and F2808 or 2<sup>16</sup>-1 for the LF2407), the CPU clock speed and, for the LF2407, the **TimerClockPrescaler** setting in the appropriate Target Preferences block. The CPU clock speed for the LF2407 is 40 MHz, for the F2808 it is 100 MHz, and for the F2812 it is 150 MHz.

| •      |      | ~    |       | ,     |

|--------|------|------|-------|-------|

| Mavir  | miim | Samo | וו בו | MAC   |

| MUALII |      | Samp | 16 11 | 11163 |

|        |      |      |       |       |

| TimerClockPrescaler Setting | C24x<br>Maximum<br>Sample<br>Time(s) | C280x<br>Maximum<br>Sample<br>Time(s) | C281x<br>Maximum<br>Sample<br>Time(s) |

|-----------------------------|--------------------------------------|---------------------------------------|---------------------------------------|

| 1                           | 0.0016                               | 42.94                                 | 28.63                                 |

| 2                           | 0.0032                               | N/A                                   | N/A                                   |

| 4                           | 0.0065                               | N/A                                   | N/A                                   |

| 8                           | 0.0131                               | N/A                                   | N/A                                   |

| 16                          | 0.0262                               | N/A                                   | N/A                                   |

| 32                          | 0.0524                               | N/A                                   | N/A                                   |

| 64                          | 0.1048                               | N/A                                   | N/A                                   |

| 128                         | 0.2097                               | N/A                                   | N/A                                   |

If all the blocks in the model inherit their sample time value, and no sample time is explicitly defined, Simulink assigns a default of 0.2 s.

#### **High-Speed Peripheral Clock**

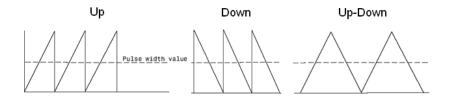

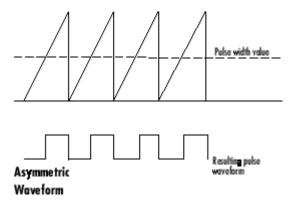

The event managers and their general-purpose timers, which drive PWM waveform generation use the high-speed peripheral clock (HISCLK). By default, this clock is always selected in the Embedded Target for TI C2000. This clock is derived from the system clock (SYSCLKOUT):

HISCLK = SYSCLKOUT / (high-speed peripheral prescaler)

The high-speed peripheral prescaler is determined by the HSPCLK bits set in SysCtrl. The default value of HSPCLK is 1, which corresponds to a high-speed peripheral prescaler value of 2.

For example, on the F2812, the HISCLK rate becomes

HISCLK = 150 MHz / 2 = 75 MHz

# **Asynchronous Interrupt Processing**

Simulink and Real-Time Workshop facilitate the modeling and generation of code for asynchronous event handling, including servicing of hardware-generated interrupts, by using the following special blocks:

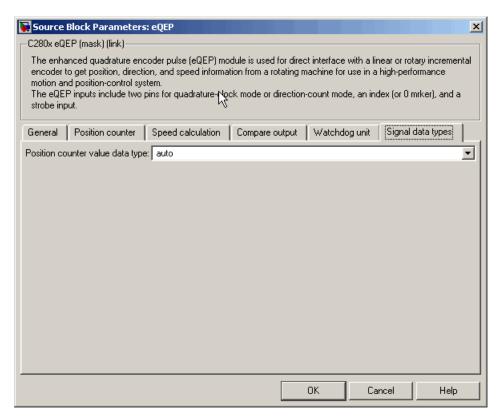

#### • Hardware Interrupt block

This block enables selected hardware interrupts, generates the corresponding interrupt service routines (ISRs), and connect them to the corresponding interrupt service vector table entries. When you connect the output of the Hardware Interrupt block to the control input of a triggered subsystem (for example, a function-call subsystem), the generated subsystem code is called from the ISRs.

Embedded Target for TI C2000 provides a Hardware Interrupt block for each of the supported processor families: C280x Hardware Interrupt and C281x Hardware Interrupt.

#### Rate Transition blocks

These blocks support data transfers between blocks running with different priorities. The built-in Simulink Rate Transition blocks can be used for this purpose.

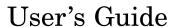

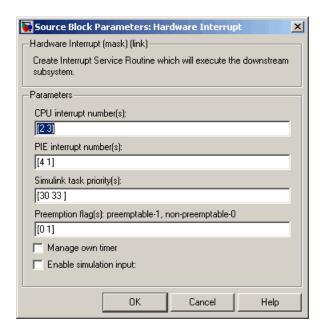

The following diagram illustrates a use case where a hardware interrupt triggers a task that also runs periodically in the context of the timer interrupt. The Hardware Interrupt block installs an ISR for a given hardware interrupt and relates the ISR to the appropriate function calls that trigger further processing. The subsystem contains the blocks that are executed asynchronously, only within the context of the hardware interrupt.

The periodic tasks, represented in the bottom half of the diagram, are clocked by a dedicated timer. The blocks are executed from within the context of a corresponding ISR, which is generated by default. The timer period is tied to the model base rate. Rate Transition blocks are used to connect the block labelled **Processing 2**, which is triggered both synchronously and asynchronously, to the model.

If there were no interaction between the synchronous and asynchronous parts of the model, the Rate Transition blocks would not be necessary.

For more information, see the section on Asynchronous Support in the Real-Time Workshop documentation.

# **Overview of Creating Models for Targeting**

After you have installed the supported development board, start MATLAB. At the MATLAB command prompt, type

c2000lib

This opens the c20001ib Simulink blockset that includes libraries containing blocks predefined for C2000 input and output devices. As needed, add the blocks to your model. See "Using the c2000lib Blockset" on page 1-20 for an example of how to use this library.

Create your real-time model for your application the same way you create any other Simulink model — by using standard blocks and C-MEX S-functions. Select blocks to build your model from the following sources:

- Appropriate Target Preferences library block, to set preferences for your target and application

- From the appropriate libraries in the c20001ib block library, to handle input and output functions for your target hardware

- From Real-Time Workshop

- From Simulink Fixed Point

- Discrete time blocks from Simulink

- From any other blockset that meets your needs and operates in the discrete time domain

## **Online Help**

To get general help for using the Embedded Target for the TI TMS320C2000 DSP Platform, use the help feature in MATLAB. At the command prompt, type

help tic2000

to list the functions and block libraries included in the Embedded Target for the TI TMS320C2000 DSP Platform. Or select **Help > Full Product Family Help** from the menu bar in the MATLAB desktop. When you see the Table of Contents in Help, select **Embedded Target for the TI C2000 DSP**.

# **Blocks to Avoid Using in Your Models**

Many blocks in the blocksets communicate with your MATLAB workspace. These blocks also generate code, but they do not work on the target as they do on your desktop — in general, they slow your signal processing application without adding instrumentation value.

For this reason, The MathWorks recommends that you *avoid* using certain blocks, such as the Scope block and some source and sink blocks, in Simulink models that you use on Embedded Target for TI C2000 DSP targets. The next table presents the blocks you should *not* use in your target models.

| Library           | Category                     | Block Name                         |

|-------------------|------------------------------|------------------------------------|

| Simulink          | Commonly Used                | Scope                              |

|                   | Sinks                        | To File                            |

|                   |                              | To Workspace                       |

|                   | Sources                      | From File                          |

|                   |                              | From Workspace                     |

| Signal Processing | Platform-Specific I/O        | From Wave Device                   |

| Blockset          |                              | From Wave File                     |

|                   |                              | To Wave Device                     |

|                   |                              | To Wave File                       |

|                   | Signal Operations            | Triggered Signal From<br>Workspace |

|                   | Signal Processing Sinks      | Signal To Workspace                |

|                   |                              | Spectrum Scope                     |

|                   |                              | Triggered to Workspace             |

|                   | Signal Processing<br>Sources | Signal From Workspace              |

#### **S-Function Builder Blocks**

Simulink S-Function Builder can be used to create and add new blocks to your model. When you generate code for your model, related source code files are added to your Code Composer Studio project.

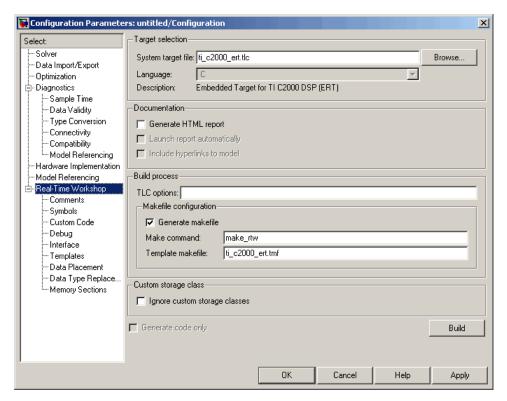

# **Setting Simulation Configuration Parameters**

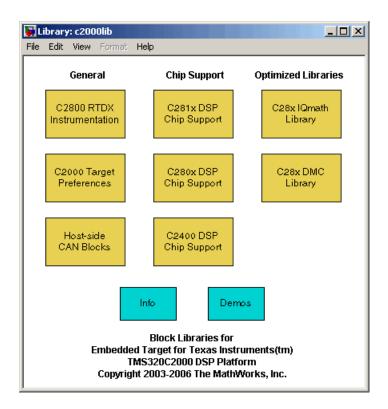

When you drag a Target Preferences block into your model, you are given the option to set basic simulation parameters automatically. (Note that this option does not appear if the Configuration Parameters dialog box is open when you drag the Target Preferences block into the model.)

To refine the automatic settings, or set the simulation parameters manually, open your model and select **Simulation > Configuration Parameters**.

If you are setting your simulation parameters manually, you must make at least the following two settings:

- You must specify discrete time by selecting Fixed-step and discrete (no continuous states) in the Solver pane of the Configuration Parameters dialog box.

- You must also specify the appropriate version of the system target file and template makefile in the **Real-Time Workshop** pane. For the Embedded Target for the TI TMS320C2000 DSP Platform, specify one of the following system target files, or click **Browse** and select from the list of targets.

```

ti_C2000_grt.tlc

ti_C2000_ert.tlc

```

The associated template filename is automatically filled in.

## System Target Types and Memory Management

There are two system target types that apply to the Embedded Target for the TI TMS320C2000 DSP Platform. These correspond to the two system target files mentioned above.

A Generic Real-Time (GRT) target (such as ti\_C2000\_grt.tlc) is the target configuration that generates model code for a real-time system as if the resulting code was going to be executed on your workstation.

An Embedded Real-Time (ERT) target (such as ti\_C2000\_ert.tlc) is the target configuration that generates model code for execution on an independent embedded real-time system. This option requires Real-Time Workshop Embedded Coder.

The ERT target for the Embedded Target for the TI TMS320C2000 DSP Platform offers memory management features that give you a way manage the performance of your code while working with limited memory resources. For more information on this, see the chapter on Memory Sections in the Real-Time Workshop Embedded Coder User's Guide.

# **Building Your Model**

With this configuration, you can generate a real-time executable and download it to your TI development board by clicking **Build** on the **Real-Time Workshop** pane. Real-Time Workshop automatically generates C code and inserts the I/O device drivers as specified by the hardware blocks in your block diagram, if any. These device drivers are inserted in the generated C code as inlined S-functions. For information about inlining S-functions, refer to your target language compiler documentation. For a complete discussion of S-functions, refer to your documentation about writing S-functions.

**Note** To build, load, and run code successfully on your target board, MATLAB must be able to locate that board in your system configuration. Make sure that the **Board Name** in your Code Composer Studio setup and the **DSPBoardLabel** in the Target Preferences block in your model match.

During the same build operation, block parameter dialog box entries are combined into a project file for CCS for your TI C2000 board. If you selected the Build and execute build action in the Target Preferences block, your makefile invokes the TI cross-compiler to build an executable file that is automatically downloaded via the parallel port to your target. After downloading the executable file to the target, the build process runs the file on the board's DSP.

**Note** After using the runtime Build option to generate and build code for your application, you must perform the following reset sequence before you can run that code on your board. If you want to rerun your application manually once it has been generated, you must also use this procedure.

#### F2812 eZdsp and F2808 eZdsp Reset Sequence

- 1 Reset the board CPU.

- **2** Load your code onto the target.

- **3** Run your code on the target.

#### LF2407 eZdsp Reset Sequence

- 1 Load your code onto the target.

- 2 Reset the board CPU.

- **3** Run your code on the target.

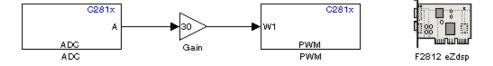

# Using the c2000lib Blockset

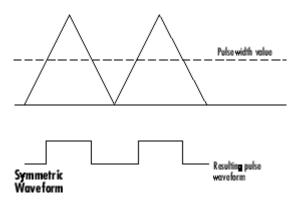

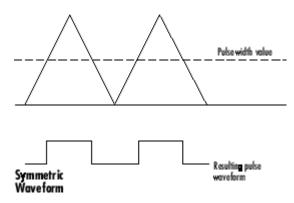

This section uses an example to demonstrate how to create a Simulink model that uses the Embedded Target for TI C2000 DSP blocks to target your board. The example creates a model that performs PWM duty cycle control via pulse width change. It uses the C2812 ADC block to sample an analog voltage and the C2812 PWM block to generate a pulse waveform. The analog voltage controls the duty cycle of the PWM and you can observe the duty cycle change on the oscilloscope. This model is also provided in the Demos library. Note that the model in the Demos library also includes a model simulation.

# **Hardware Setup**

The following hardware is needed for this example:

- Spectrum Digital eZdsp F2812

- Function generator

- Oscilloscope and probes

To connect the hardware:

- 1 Connect the function generator output to the ADC input ADCINA0 on the eZdsp F2812.

- **2** Connect the output of PWM1 on the eZdsp F2812 to the analog input of the oscilloscope.

- **3** Connect VREFLO to AGND on the eZdsp F2812. See the section on the Analog Interface in Chapter 2 of the  $eZdsp^{TM}$  F2812 Technical Reference, available from the Spectrum Digital Web site at http://c2000.spectrumdigital.com/ezf2812/

# Starting the c2000lib Library

At the MATLAB prompt, type

c2000lib

to open the c2000lib library blockset, which contains libraries of blocks designed for targeting your board.

The libraries are in three groups, plus Info and Demos blocks.

#### General

- C2800 RTDX Instrumentation (rtdxBlocks) Blocks for adding RTDX communications channels to Simulink models. See the tutorial in the Link for Code Composer Studio Development Tools documentation for an example of using these blocks.

- C2000 Target Preferences (c2000tgtpreflib) Blocks to specify target preferences and options. You do not connect this block to any other block in your model.

- Host-side CAN Blocks (c2000canlib) Blocks to configure CAN message blocks and Vector CAN driver blocks

#### **Chip Support**

- C281x DSP Chip Support (c281xdspchiplib) Blocks to configure the codec on the F2812 eZdsp DSK or on C281x-based custom boards

- C280x DSP Chip Support (c280xdspchiplib) Blocks to configure the codec on the F2808 eZdsp DSK or on C280x-based custom boards

- C2400 DSP Chip Support (c2400dspchiplib) Blocks to configure the codec on the LF2407 eZdsp DSK or on the LF2407 DSP

#### **Optimized Libraries**

- C28x IQmath Library (tiiqmathlib) Fixed-point math blocks for use with C28x targets

- C28x DMC Library (c28xdmclib) Fixed-point math blocks for digital motor control with C28x DSPs

#### Other Blocks

- Info block Online help

- Demos block Demos window

For more information on the blocks in each library, refer to their reference pages.

# **Setting Up the Model**

Preliminary tasks for setting up a new model include adding a Target Preferences block, setting or verifying Target Preferences, and setting the simulation parameters.

- 1 In the Library: c2000lib window, select File > New > Model to create a new Simulink model.

- **2** In the Library: c2000lib window, double-click the C2000 Target Preferences library block.

- **3** From the Target Preferences Library window, drag the F2812 eZdsp block into your new model.

F2812 eZdsp

The following query asks if you want preferences to be set automatically.

**4** Click **Yes** to allow automatic setup. The following settings are made, referenced in the table below by their locations in the **Simulation > Configuration Parameters** dialog box:

| Pane                       | Field                                        | Setting          |

|----------------------------|----------------------------------------------|------------------|

| Solver                     | Stop time                                    | inf              |

| Solver                     | Туре                                         | Fixed-step       |

| Data<br>Import/Export      | Save to workspace - Time                     | Off (cleared)    |

| Data<br>Import/Export      | Save to workspace -<br>Output                | Off (cleared)    |

| Hardware<br>Implementation | Device type                                  | TI C2000         |

| Real-Time<br>Workshop      | Target configuration -<br>System target file | ti_c2000_grt.tlc |

| Real-Time<br>Workshop      | Target configuration -<br>Template makefile  | ti_c2000_grt.tmf |

**Note** Generated code does not honor Simulink stop time from the simulation. Stop time is interpreted as inf. To implement a stop in generated code, you must put a Stop Simulation block in your model.

**Note** One Target Preferences block must be in each target model at the top level. It does not connect to any other blocks, but stands alone to set the target preferences for the model.

- 5 From your model's main menu, select Simulation > Configuration

Parameters to verify and set the simulation parameters for this model.

Parameters you set in this dialog box belong to the model you are building.

They are saved with the model and stored in the model file. Refer to your

Simulink documentation for information on the Configuration Parameters

dialog box.

- **6** Use the **Real-Time Workshop** pane to set options for the real-time model. Refer to your Real-Time Workshop documentation for detailed information on the **Real-Time Workshop** pane options.

- System target file. Clicking Browse opens the System target file browser where you select ti\_c2000\_grt.tlc or ti\_c2000\_ert.tlc. When you select your target configuration, Real-Time Workshop chooses the appropriate system target file, template makefile, and make command. You can also enter the target configuration filename, and Real-Time Workshop will fill in the Template makefile and Make command selections.

- Make command. When you generate code from your digital signal processing application, use the standard command make\_rtw. Enter make\_rtw for the Make command.

- Template makefile. When you select the **System target file**, Real-Time Workshop automatically selects the appropriate template makefile: ti\_c2000\_grt.tmf or ti\_c2000\_ert.tmf.

• Generate code only. This option does not apply to targeting with the Embedded Target for TI C2000 DSP. To generate source code without building and executing the code on your target, open the Target Preferences block in your model and select Generate code only as the BuildAction (BuildOptions > RunTimeOptions > BuildAction).

For all other Real-Time Workshop options, leave the default values for this example.

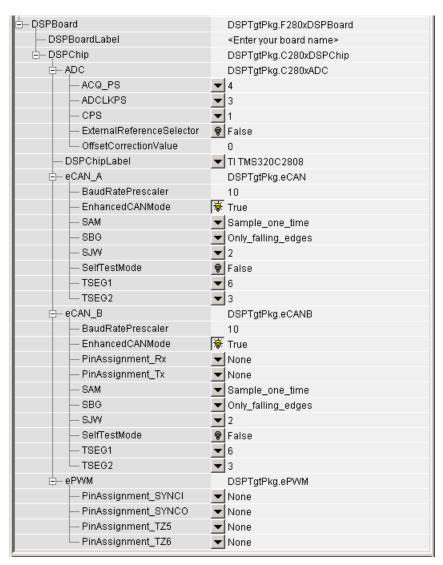

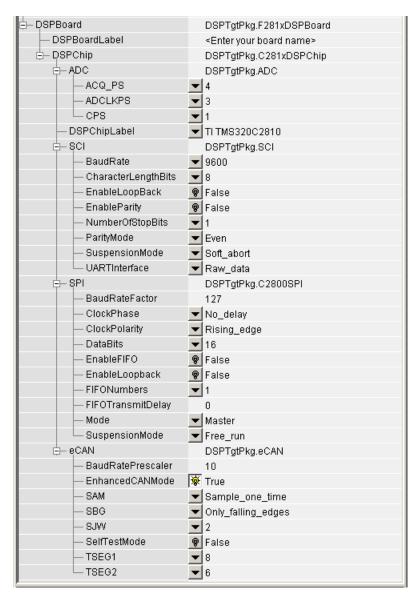

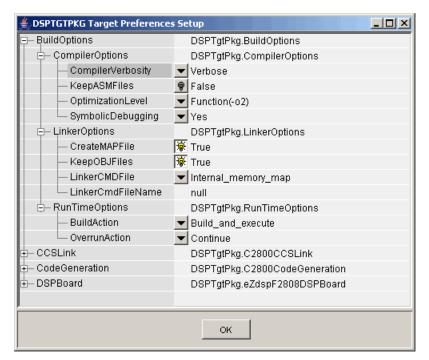

**7** Set the Target Preferences by double-clicking the F2812 eZdsp block and adjust these parameters. For descriptions of these fields, see the F2812 eZdsp reference page.

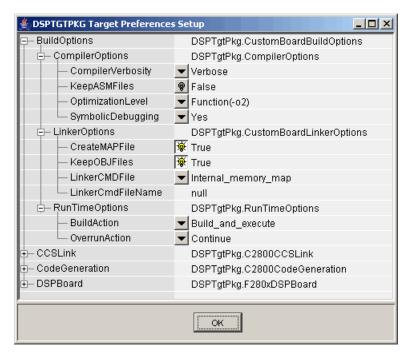

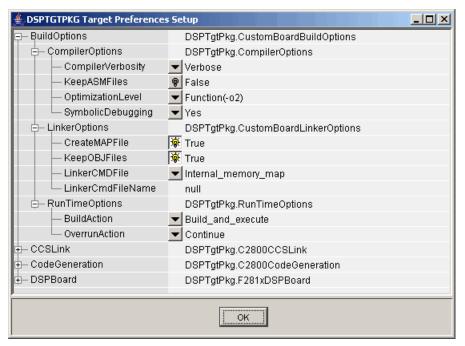

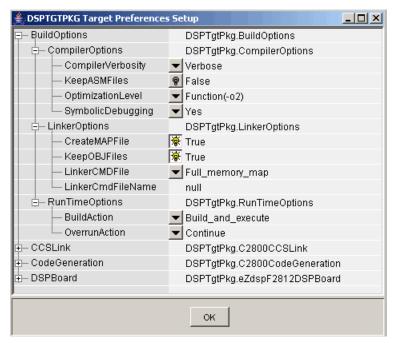

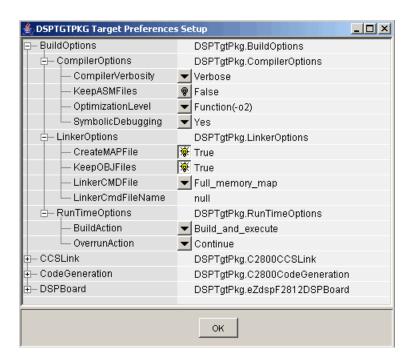

#### **Build Options**

| Subfield                | Field             | Setting           |

|-------------------------|-------------------|-------------------|

| <b>Compiler Options</b> | CompilerVerbosity | Verbose           |

|                         | KeepASMFiles      | False             |

|                         | OptimizationLevel | Function(-o2)     |

|                         | SymbolicDebugging | Yes               |

| Linker Options          | CreateMAPFile     | True              |

|                         | KeepOBJFiles      | True              |

|                         | LinkerCMDFile     | Full_memory_map   |

| <b>RunTime Options</b>  | BuildAction       | Build_and_execute |

|                         | OverrunAction     | Continue          |

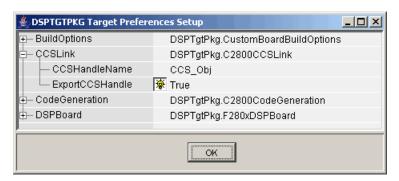

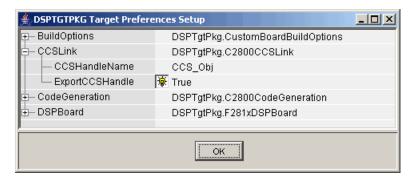

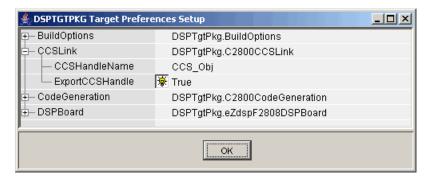

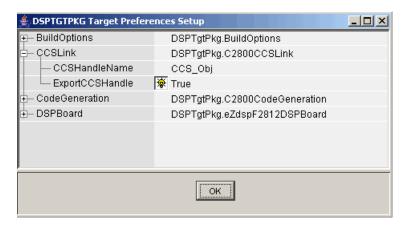

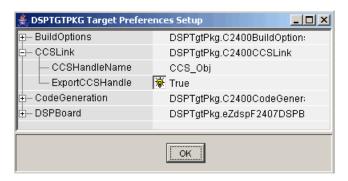

# **CCSLink Options**

| Field           | Setting |

|-----------------|---------|

| CCSHandleName   | CCS_0bj |

| ExportCCSHandle | True    |

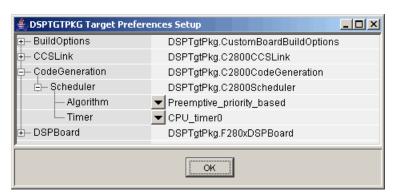

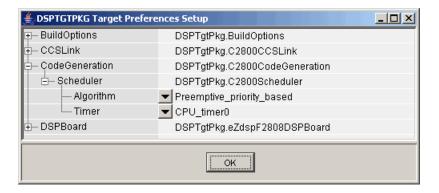

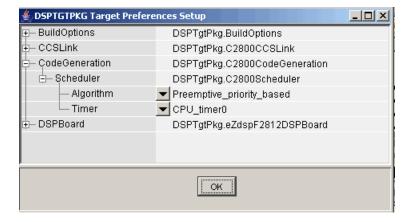

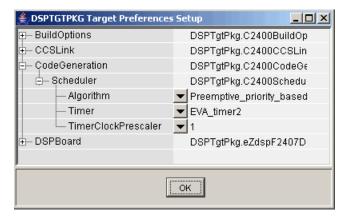

# **CodeGeneration Options**

| Subfield  | Field Setting |                           |

|-----------|---------------|---------------------------|

| Scheduler | Algorithm     | Preemptive_priority_based |

|           | Timer         | CPU_timer0                |

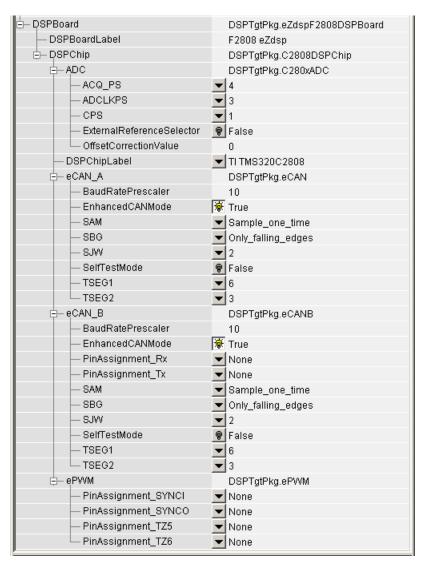

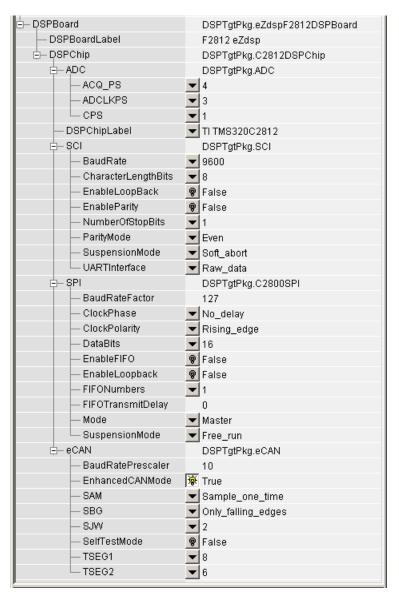

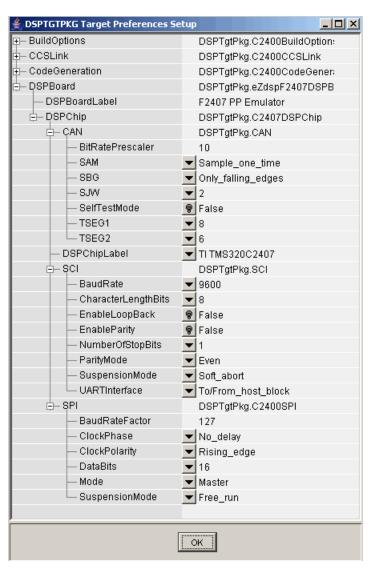

# **DSPBoard Options**

| Subfield        | Field             | Setting                            |

|-----------------|-------------------|------------------------------------|

| DSP Board Label | DSPBoardLabel     | F2812 PP Emulator (see Note below) |

| DSP Chip        | DSPChipLabel      | TI TMS320C2812                     |

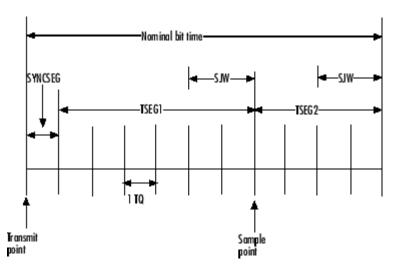

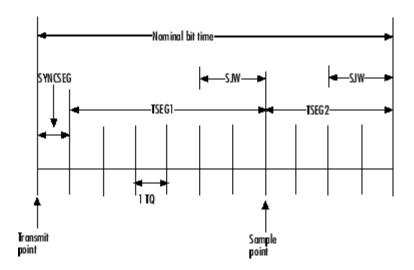

| eCAN            | BaudRatePrescaler | 10                                 |

|                 | EnhancedCANMode   | True                               |

|                 | SAM               | Sample_one_time                    |

|                 | SBJ               | Only_falling_edges                 |

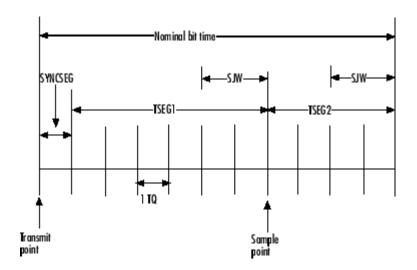

|                 | SJW               | 2                                  |

|                 | SelfTestMode      | False                              |

|                 | TSEG1             | 8                                  |

|                 | TSEG2             | 6                                  |

**Note** If the board label in your Code Composer Studio setup differs from the default DSP Board Label shown in the Target Preferences block, you can change the default setting. This would ensure that whenever you drag a Target Preferences block into a new model, the DSP Board Label of your model will match the label in your Code Composer Studio setup.

Open the C2000 Target Preferences library. Double-click the appropriate Target Preferences block. Click **DSP Board** and change the text in the DSP Board Label right column to the desired string. Click **OK** to close the Target Preferences block and then close the library to save your change.

# Adding Blocks to the Model

1 Double-click the C281x DSP Chip Support Library to open it.

- **2** Drag the C281x ADC block into your model. Double-click the ADC block in the model and set **Sample time** to 64/80000. Use the default values for all other fields. Refer to the C281x ADC reference page for information on these fields.

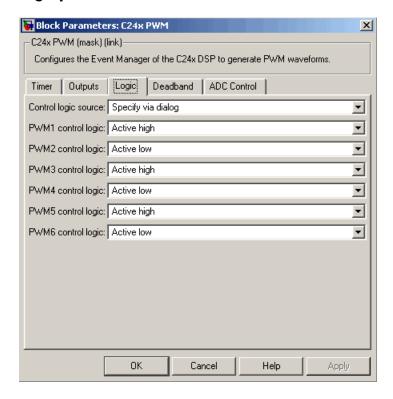

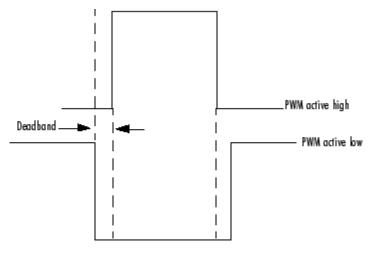

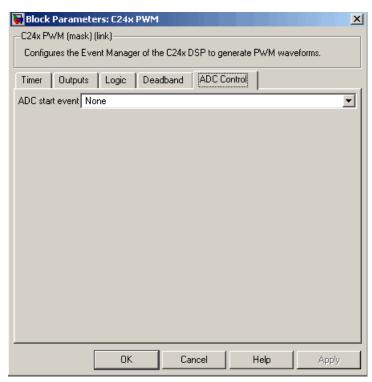

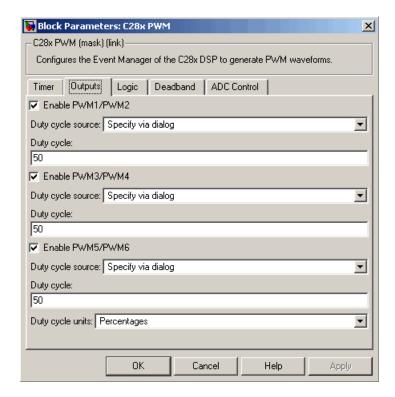

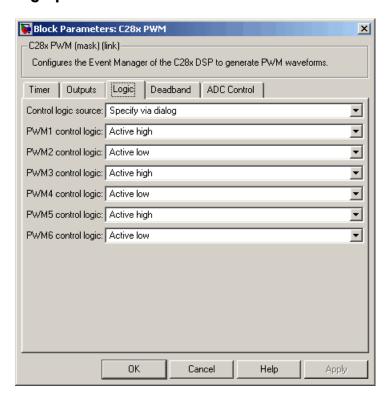

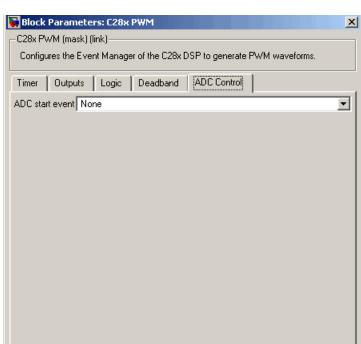

- **3** Drag the C281x PWM block into your model. Double-click the PWM block in the model and set the following parameters. Refer to the C281x PWM reference page for information on these fields.

| Pane        | Field                            | Parameter          |

|-------------|----------------------------------|--------------------|

| Timer       | Module                           | A                  |

|             | Waveform period source           | Specify via dialog |

|             | Waveform period units            | Clock cycles       |

|             | Waveform period                  | 64000              |

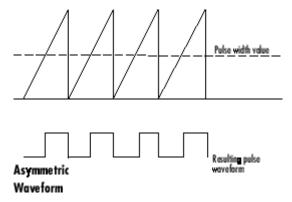

|             | Waveform type                    | Asymmetric         |

| Outputs     | Enable<br>PWM1/PWM2              | Selected           |

|             | Duty cycle source                | Input port         |

| Logic       | PWM1 control logic               | Active high        |

|             | PWM2 control logic               | Active low         |

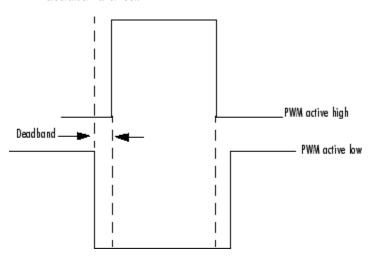

| Deadband    | Use<br>deadband for<br>PWM1/PWM2 | Selected           |

|             | Deadband<br>prescaler            | 16                 |

|             | Deadband<br>period               | 12                 |

| ADC Control | ADC start event                  | Period interrupt   |

**<sup>4</sup>** Type Simulink at the MATLAB command line to open the Simulink Library browser. Drag a Gain block from the Math Operations library into your model. Double-click the Gain block in the model and set the following parameters in the Function Block Parameters dialog box. Click **OK**.

| Pane                    | Field                             | Parameter          |

|-------------------------|-----------------------------------|--------------------|

| Main                    | Gain                              | 30                 |

|                         | Multiplication                    | Element-wise(K.*u) |

|                         | Sample time                       | -1                 |

| Signal Data Types       | Output data type mode             | Specify via dialog |

|                         | Output data type                  | uint(16)           |

|                         | Round integer calculations toward | Floor              |

| Parameter Data<br>Types | Parameter data type mode          | Same as input      |

**5** Connect the ADC block to the Gain block and the Gain block to the PWM block as shown:

# Generating Code from the Model

This section summarizes how to generate code from your real-time model. For details about generating code from models in Real-Time Workshop, refer to the Real-Time Workshop documentation.

You start the automatic code generation process from the Simulink model window by clicking **Build** in the **Real-Time Workshop** pane of the Configuration Parameters dialog. Other ways of starting the code generation process are by clicking the **Build all** button on the toolbar of your model, or by pressing the keyboard shortcut, **Ctrl+B**, while your model is open and in focus.

The code building process consists of these steps:

1 Real-Time Workshop invokes the function make\_rtw to start the Real-Time Workshop build procedure for a block diagram. make\_rtw invokes the Target Language Compiler to generate the code and then invokes the language-specific make procedure.

2 gmake builds file modelname.out. Depending on the build options you select in the Simulation Parameters dialog box, gmake can initiate the sequence that downloads and executes the model on your TI target board.

# Creating Code Composer Studio Projects Without Loading

To create projects in CCS without loading files to your target:

- 1 In the **Real-Time Workshop** pane in the Simulation Parameters dialog box, select ti c2000.tlc as the system target file.

- 2 Select Create\_CCS\_Project for the **BuildAction** in the Target Preferences block. Note that the Build and Build\_and\_execute options create CCS projects as well.

- **3** Set the other Target Preferences options, including those for **CCSLink**. On the **Real-Time Workshop** pane of the Simulation Parameters dialog box, click **Build** to build your new CCS project.

Real-Time Workshop and the Embedded Target for TI C2000 DSP generate all the files for your project in CCS and create a new project in the IDE. Your new project is named for the model you built.

In CCS you see your project with the files in place in the directory tree.

# Using the IQmath Library

About the IQmath Library (p. 2-2)

Fixed-Point Numbers (p. 2-4)

Building Models (p. 2-9)

Introduces the IQmath Library

Representation of fixed-point numbers in the IQmath Library

Issues to consider when you build models with the IQmath Library

# **About the IQmath Library**

The IQmath Library provides blocks that perform processor-optimized, fixed-point mathematical operations. The blocks in the C28x IQmath Library correspond to functions in the Texas Instruments C28x IQmath Library assembly-code library, which target the TI C28x family of digital signal processors.

**Note** The implementation of this library for the TI C28x processor produces the same simulation and code-generation output as the TI version of this library, but it does not use a global Q value, as does the TI version. The Q format is dynamically adjusted based on the Q format of the input data.

The IQmath Library blocks generally input and output fixed-point data types and use numbers in Q format. The C28x IQmath Library block reference pages discuss the data types accepted and produced by each block in the library. For more information on fixed-point numbers and Q format, see

- "Fixed-Point Numbers" on page 2-4. In addition, see the Simulink Fixed Point documentation, which includes more information on fixed-point data types and scaling and precision issues.

- "Q Format Notation" on page 2-5

You can use these blocks with some core Simulink blocks and Simulink Fixed Point blocks to run simulations in Simulink models before generating code. Once you develop your model, you can invoke Real-Time Workshop to generate equivalent code that is optimized to run on a TI C28x DSP. During code generation, a call is made to the IQmath Library for each IQmath Library block in your model to create target-optimized code. To learn more about creating models that include both IQmath Library blocks and blocks from other blocksets, refer to "Building Models" on page 2-9.

## **Common Characteristics**

The following characteristics are common to all IQmath Library blocks:

· Sample times are inherited from driving blocks.

- Blocks are single rate.

- Parameters are not tunable.

- All blocks support discrete sample times.

To learn more about characteristics particular to each block in the library, see "C28x IQmath Library (tiiqmathlib)" on page 3-10 for links to the individual block reference pages.

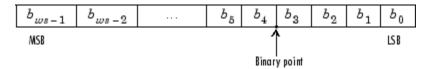

# **Fixed-Point Numbers**

In digital hardware, numbers are stored in binary words. A binary word is a fixed-length sequence of binary digits (1's and 0's). How hardware components or software functions interpret this sequence of 1's and 0's is defined by the data type.

Binary numbers are used to represent either fixed-point or floating-point data types. A fixed-point data type is characterized by the word size in bits, the binary point, and whether it is signed or unsigned. The position of the binary point is the means by which fixed-point values are scaled and interpreted.

For example, a binary representation of a fractional fixed-point number (either signed or unsigned) is shown below:

#### where

- *b*; is the *i*th binary digit.

- ws is the word size in bits.

- $b_{ms-1}$  is the location of the most significant (highest) bit (MSB).

- $b_0$  is the location of the least significant (lowest) bit (LSB).

- The binary point is shown four places to the left of the LSB. In this example, therefore, the number is said to have four fractional bits, or a fraction length of 4.

# **Signed Fixed-Point Numbers**

Signed binary fixed-point numbers are typically represented in one of three ways:

- Sign/magnitude

- One's complement

• Two's complement

Two's complement is the most common representation of signed fixed-point numbers and is used by TI digital signal processors.

Negation using signed two's complement representation consists of a bit inversion (translation into one's complement) followed by the binary addition of a 1. For example, the two's complement of 000101 is 111011, as follows:

000101 ->111010 (bit inversion) ->111011 (binary addition of a 1 to the LSB)

#### **Q** Format Notation

The position of the binary point in a fixed-point number determines how you interpret the scaling of the number. When it performs basic arithmetic such as addition or subtraction, hardware uses the same logic circuits regardless of the value of the scale factor. In essence, the logic circuits have no knowledge of a binary point. They perform signed or unsigned integer arithmetic — as if the binary point is to the right of  $b_0$ . Therefore, you determine the binary point.

In the IQmath Library, the position of the binary point in the signed, fixed-point data types is expressed in and designated by Q format notation. This fixed-point notation takes the form

Qm.n

where

- Q designates that the number is in Q format notation the Texas Instruments representation for signed fixed-point numbers.

- *m* is the number of bits used to designate the two's complement integer portion of the number.

- *n* is the number of bits used to designate the two's complement fractional portion of the number, or the number of bits to the right of the binary point.

In Q format, the most significant bit is always designated as the sign bit. Representing a signed fixed-point data type in Q format always requires m+n+1 bits to account for the sign.

**Note** The range and resolution varies for different Q formats. For specific details, see Section 3.2 in the *Texas Instruments C28x Foundation Software*, *IQmath Library Module User's Guide*.

When converting from Q format to floating-point format, the accuracy of the conversion depends on the values and formats of the numbers. For example, for single-precision floating-point numbers, which use 24 bits, the resolution of the corresponding 32-bit number cannot be attained. The 24-bit number approximates its value by truncating the lower end. For example:

```

32-bit integer 11110000 11001100 10101010 00001111

Single-precision float +1.1110000 11001100 10101010 x 231

Corresponding value 11110000 11001100 10101010 00000000

```

#### Example - Q.15

For example, a signed 16-bit number with n = 15 bits to the right of the binary point is expressed as

```

Q0.15

```

in this notation. This is (1 sign bit) + (m = 0 integer bits) + (n = 15 fractional bits) = 16 bits total in the data type. In Q format notation, the m = 0 is often implied, as in

```

Q.15

```

In Simulink Fixed Point, this data type is expressed as

```

sfrac16

```

or

```

sfix16_En15

```

In the Filter Design Toolbox, this data type is expressed as

```

[16 15]

```

### Example - Q1.30

Multiplying two Q.15 numbers yields a product that is a signed 32-bit data type with n=30 bits to the right of the binary point. One bit is the designated sign bit, thereby forcing m to be 1:

```

m+n+1 = 1+30+1 = 32 bits total

```

Therefore, this number is expressed as

Q1.30

In Simulink Fixed Point, this data type is expressed as

In the Filter Design Toolbox, this data type is expressed as

[32 30]

### **Example - Q-2.17**

Consider a signed 16-bit number with a scaling of  $2^{(-17)}$ . This requires n = 17 bits to the right of the binary point, meaning that the most significant bit is a *sign-extended* bit.

Sign extension fills additional bits with the value of the MSB. For example, consider a 4-bit two's complement number 1011. When this number is extended to 7 bits with sign extension, the number becomes 1111101 and the value of the number remains the same.

One bit is the designated sign bit, forcing m to be -2:

$$m+n+1 = -2+17+1 = 16$$

bits total

Therefore, this number is expressed as

Q-2.17

In Simulink Fixed Point, this data type is expressed as

sfix16 En17

In the Filter Design Toolbox, this data type is expressed as

[16 17]

### **Example - Q17.-2**

Consider a signed 16-bit number with a scaling of 2<sup>(2)</sup> or 4. This means that the binary point is implied to be 2 bits to the right of the 16 bits, or that there are n = -2 bits to the right of the binary point. One bit must be the sign bit, thereby forcing m to be 17:

$$m+n+1 = 17+(-2)+1 = 16$$

Therefore, this number is expressed as

Q17.-2

In Simulink Fixed Point, this data type is expressed as

sfix16\_E2

In the Filter Design Toolbox, this data type is expressed as

[16 -2]

# **Building Models**

You can use IQmath Library blocks in models along with certain core Simulink, Simulink Fixed Point, and other blockset blocks. This section discusses issues you should consider when building a model with blocks from these different libraries.

# **Converting Data Types**

As always, it is vital to make sure that any blocks you connect in a model have compatible input and output data types. In most cases, IQmath Library blocks handle only a limited number of specific data types. You can refer to any block reference page in the alphabetical block reference for a discussion of the data types that the block accepts and produces.

When you connect IQmath Library blocks and Simulink Fixed Point blocks, you often need to set the data type and scaling in the block parameters of the Simulink Fixed Point block to match the data type of the IQmath Library block. Many Simulink Fixed Point blocks allow you to set their data type and scaling through inheritance from the driving block, or through backpropagation from the next block. This can be a good way to set the data type of a Simulink Fixed Point block to match a connected IQmath Library block.

Some Signal Processing Blockset blocks and core Simulink blocks also accept fixed-point data types. Make the appropriate settings in these blocks' parameters when you connect them to an IQmath Library block.

# **Using Sources and Sinks**

The IQmath Library does not include source or sink blocks. Use source or sink blocks from the core Simulink library or Simulink Fixed Point in your models with IQmath Library blocks.

# **Choosing Blocks to Optimize Code**

In some cases, blocks that perform similar functions appear in more than one blockset. For example, both the IQmath Library and Simulink Fixed Point have a Multiply block. When you are building a model to run on C2000 DSP, choosing the block from the IQmath Library always yields better

optimized code. You can use a similar block from another library if it gives you functionality that the IQmath Library block does not support, but you will generate code that is less optimized.

# Blocks — By Category

C2000 Target Preferences Library (c2000tgtpreflib) (p. 3-2)

Host-side CAN Blocks (c2000canlib) (p. 3-3)

C2000 RTDX Instrumentation Library (rtdxBlocks) (p. 3-4)

C2400 DSP Chip Support Library (c2400dspchiplib) (p. 3-5)

C280x DSP Chip Support Library (c280xdspchiplib) (p. 3-6)

C281x DSP Chip Support Library (c281xdspchiplib) (p. 3-7)

C28x Digital Motor Control Library (c28xdmclib) (p. 3-9)

C28x IQmath Library (tiiqmathlib) (p. 3-10)

Target preference blocks for C2000

boards

Host-side CAN blocks

RTDX blocks for C2000 boards

Blocks that support C24x boards

Blocks that support C280x boards

Blocks that support C281x boards

Blocks that represent the functionality of the TI C28x DMC Library

Blocks that represent the functionality of the TI IQmath Library

# C2000 Target Preferences Library (c2000tgtpreflib)

Custom C280x Board Target preferences for custom C280x

board

Custom C281x Board Target preferences for custom C281x

oard

F2808 eZdsp DSK target preferences

F2812 eZdsp DSK target preferences

LF2407 eZdsp DSK target

preferences

# Host-side CAN Blocks (c2000canlib)

Refer to the CAN Blockset documentation for information on these blocks.

Vector CAN Configuration Configure a CAN channel (either

hardware or virtual) for use with

Vector-Informatik drivers

Vector CAN Receive Read CAN frames from a Vector CAN

channel

Vector CAN Transmit Transmit CAN frames on a Vector CAN

channel

CAN Message Packing Map Simulink signals to CAN messages.

CAN Message Packing (CANdb) Pack Simulink signals into CAN

messages defined by CANdb

CAN Message Filter Dispatch message processing based on

message ID

CAN Message Unpacking Inspect and unpack the individual fields

in a CAN message

CAN Message Unpacking

(CANdb)

Decompose a CAN frame into its

constituent signals

# C2000 RTDX Instrumentation Library (rtdxBlocks)

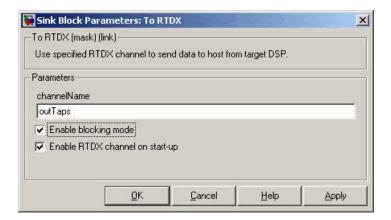

From RTDX To RTDX Add RTDX input channel Add RTDX output channel

# C2400 DSP Chip Support Library (c2400dspchiplib)

C24x ADC Analog-to-digital converter (ADC)

C24x CAN Receive Enhanced Control Area Network

receive mailbox

C24x CAN Transmit Enhanced Control Area Network

transmit mailbox

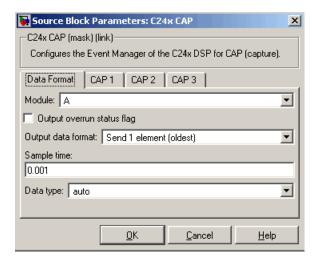

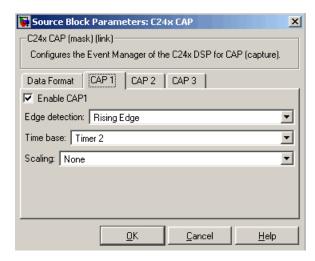

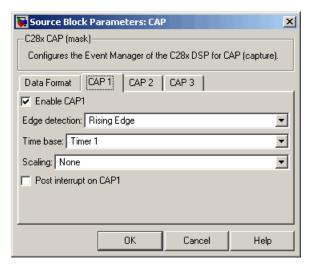

C24x CAP Receive and log capture input pin

transitions

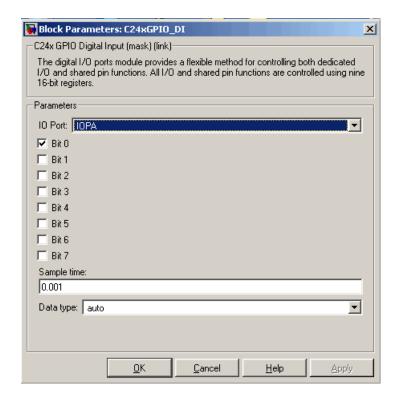

C24x GPIO Digital Input General-purpose I/O pins for digital

input

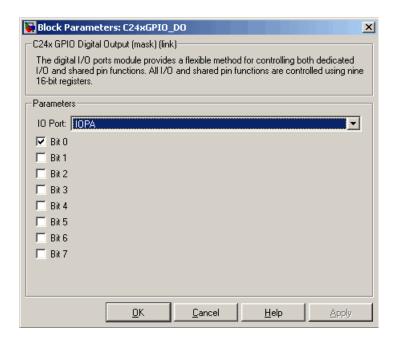

C24x GPIO Digital Output General-purpose I/O pins for digital

output

C24x PWM Pulse wave modulators (PWMs)

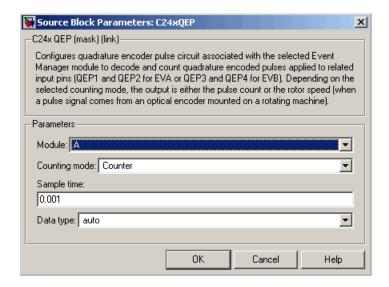

C24x QEP Quadrature encoder pulse circuit

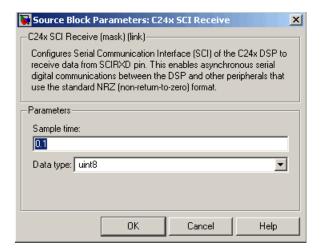

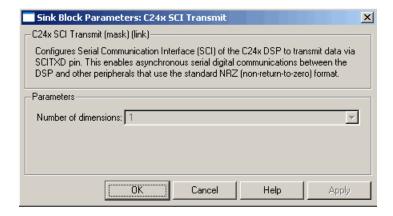

C24x SCI Receive Receive data on the target via serial

communications interface (SCI) from

the host

C24x SCI Transmit Transmit data on target via serial

communications interface (SCI) from

host

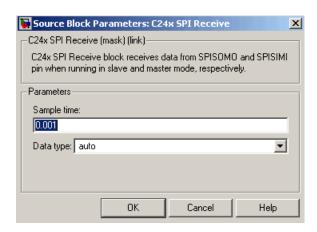

C24x SPI Receive Receive data via the serial peripheral

interface (SPI) on target

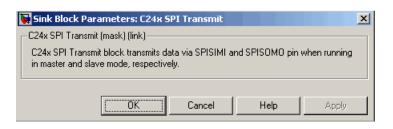

C24x SPI Transmit Transmit data via the serial

peripheral interface (SPI) to host

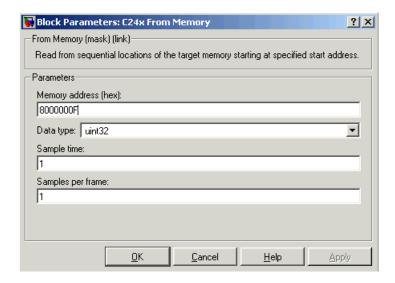

From Memory Retrieve data from target memory

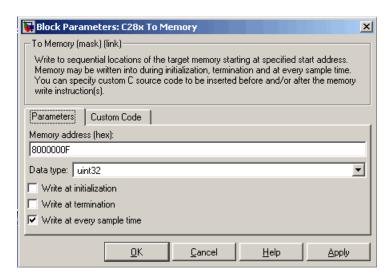

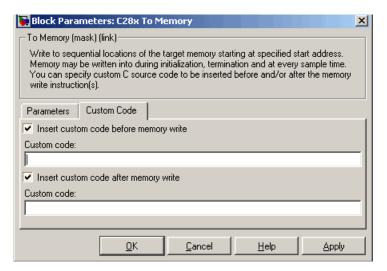

To Memory Write data to target memory

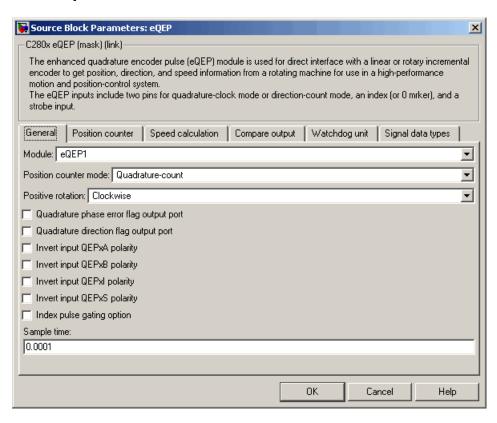

# C280x DSP Chip Support Library (c280xdspchiplib)

C280x ADC Analog-to-digital converter (ADC)

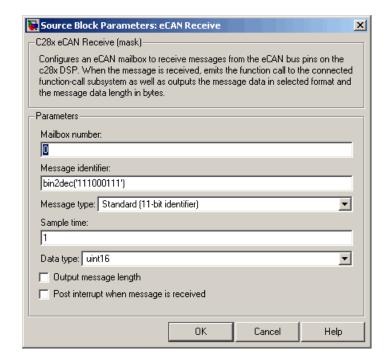

C280x eCAN Receive Enhanced Control Area Network

receive mailbox

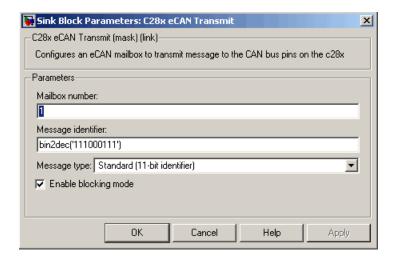

C280x eCAN Transmit Enhanced Control Area Network

transmit mailbox

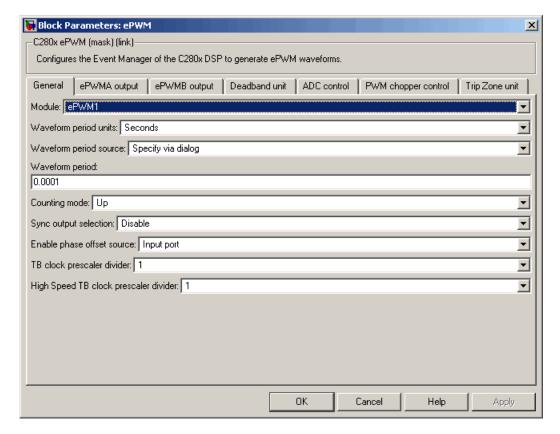

C280x ePWM Configures the C280x Event

Manager to generate Enhanced Pulse Width Modulator (ePWM)

waveforms.

C280x eQEP Quadrature encoder pulse circuit

C280x Hardware Interrupt Create an Interrupt Service Routine

to handle hardware interrupts

From Memory Retrieve data from target memory

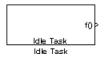

Idle Task Create free-running task that

executes downstream subsystem

To Memory Write data to target memory

# C281x DSP Chip Support Library (c281xdspchiplib)

C281x ADC Analog-to-digital converter (ADC)

C281x CAP Receive and log capture input pin

transitions

C281x eCAN Receive Enhanced Control Area Network

receive mailbox

C281x eCAN Transmit Enhanced Control Area Network

transmit mailbox

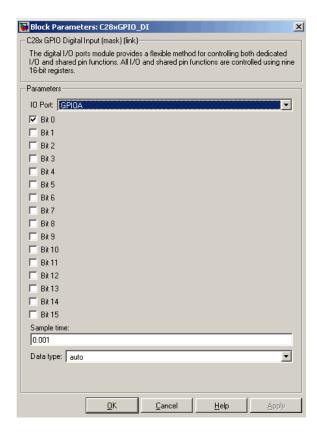

C281x GPIO Digital Input General-purpose I/O pins for digital

input

C281x GPIO Digital Output General-purpose I/O pins for digital

output

C281x Hardware Interrupt Create an Interrupt Service Routine

to handle hardware interrupts

C281x PWM Pulse wave modulators (PWMs)

C281x QEP Quadrature encoder pulse circuit

C281x SCI Receive Receive data on target via serial

communications interface (SCI) from

host

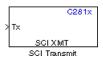

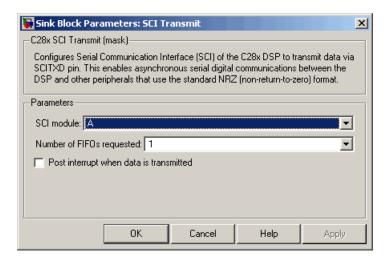

C281x SCI Transmit Transmit data on target via serial

$communications\ interface\ (SCI)\ from$

host

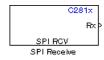

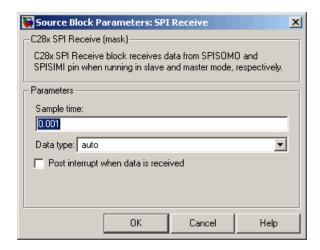

C281x SPI Receive Receive data via the serial peripheral

interface (SPI) on the target

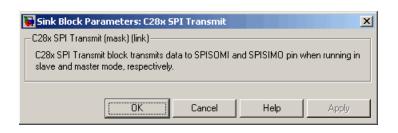

C281x SPI Transmit Transmit data via the serial

peripheral interface (SPI) to the host

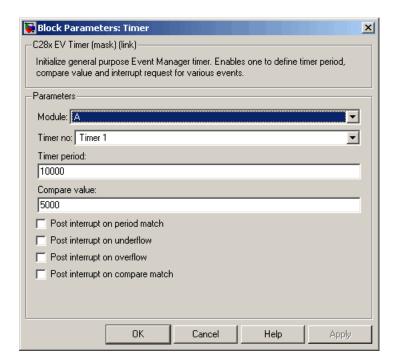

C281x Timer Configure up to four general-purpose,

$stand-alone\ Event\ Manager\ timers.$

From Memory Retrieve data from target memory

Create free-running task that executes downstream subsystem Idle Task

To Memory Write data to target memory

# C28x Digital Motor Control Library (c28xdmclib)

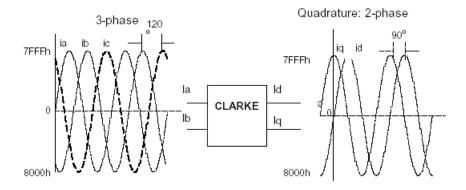

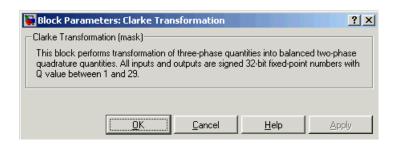

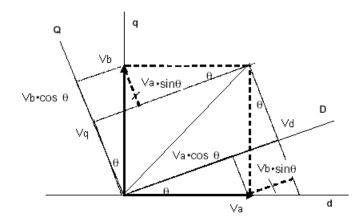

Clarke Transformation Convert balanced three-phase

quantities to balanced two-phase

quadrature quantities

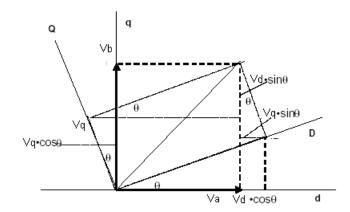

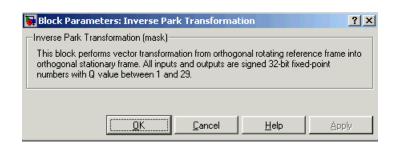

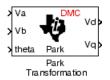

Inverse Park Transformation Convert rotating reference frame

vectors to two-phase stationary

reference frame

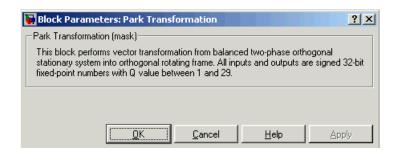

Park Transformation Convert two-phase stationary

system vectors to rotating system

vectors

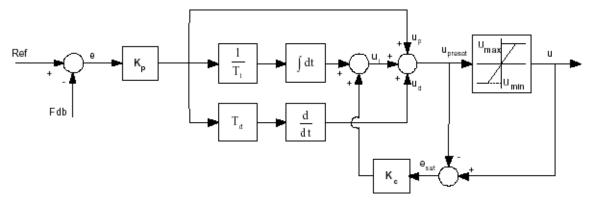

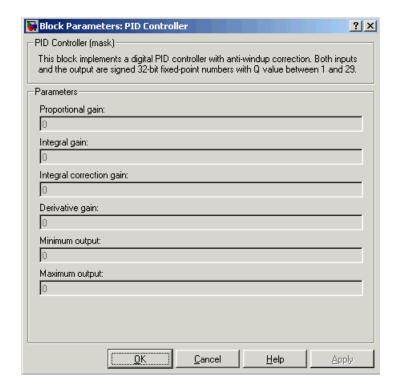

PID Controller Digital PID controller

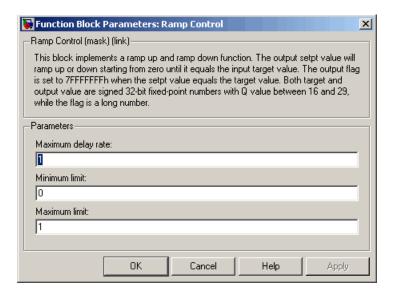

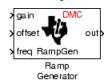

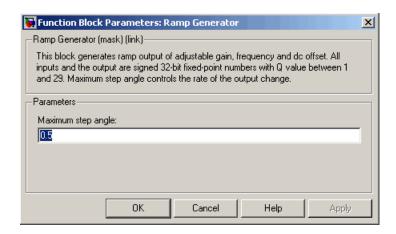

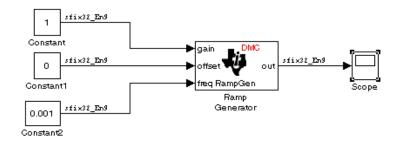

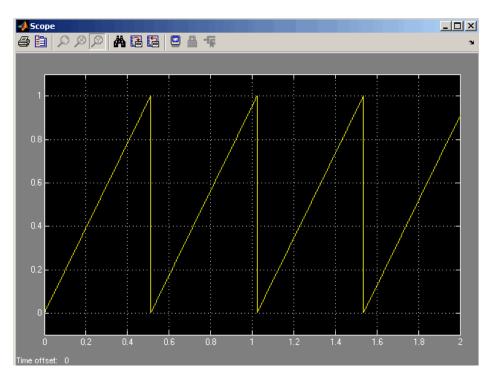

Ramp Control Create a ramp-up and ramp-down

function

Ramp Generator Generate ramp output

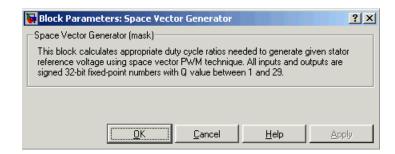

Space Vector Generator Duty ratios for stator reference

voltage

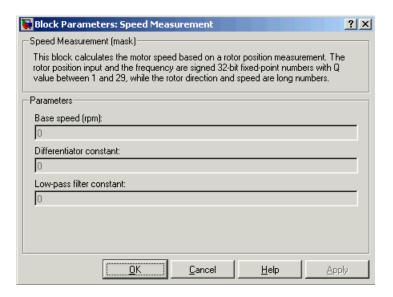

Speed Measurement Motor speed

# C28x IQmath Library (tiigmathlib)

Absolute IQN Absolute value

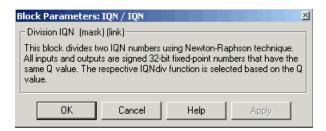

Arctangent IQN Four-quadrant arc tangent Division IQN Divide two IQ numbers

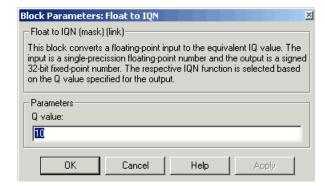

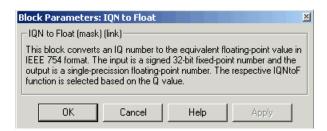

Float to IQN Convert floating-point number to IQ

number

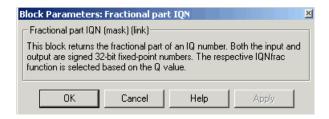

Fractional part IQN Fractional part of IQ number

Fractional part IQN x int32 Fractional part of result of

multiplying IQ number and long

integer

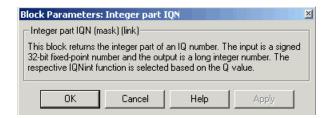

Integer part IQN Integer part of IQ number

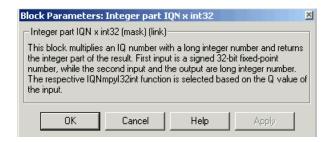

Integer part IQN x int32 Integer part of result of multiplying

IQ number and long integer

IQN to Float Convert IQ number to floating-point

number

IQN x int32 Multiply IQ number with long

integer

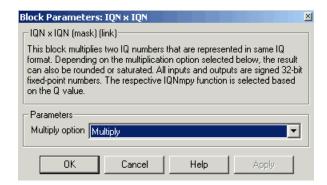

IQN x IQN Multiply two IQ numbers with same

Q format

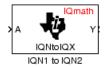

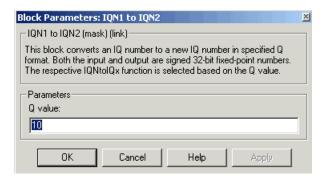

IQN1 to IQN2 Convert IQ number to different Q

format

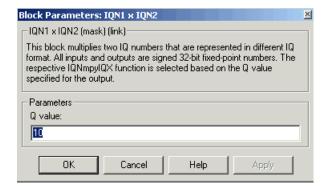

IQN1 x IQN2 Multiply two IQ numbers with

different Q formats

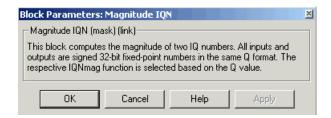

Magnitude IQN Magnitude of two orthogonal IQ

numbers

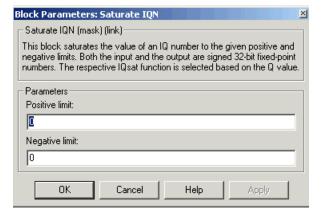

Saturate IQN Saturate an IQ number

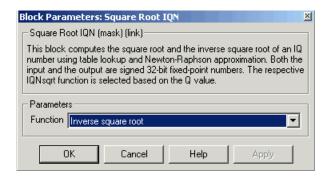

Square Root IQN Square root or inverse square root

of IQ number

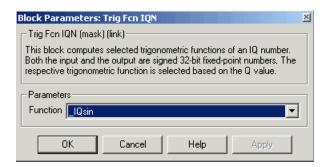

Trig Fcn IQN Sine, cosine, or arc tangent of IQ

number

# Blocks — Alphabetical List

# **Absolute IQN**

**Purpose**

Absolute value

Library

tiigmathlib in Embedded Target for TI C2000 DSP

### **Description**

This block computes the absolute value of an IQ number input. The output is also an IQ number.

**Note** The implementation of this block does not call the corresponding Texas Instruments library function during code generation. The TI function uses a global Q setting and the MathWorks code used by this block dynamically adjusts the Q format based on the block input. See "About the IQmath Library" on page 2-2 for more information.

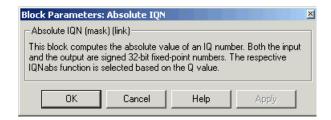

## Dialog Box

#### See Also

Arctangent IQN, Division IQN, Float to IQN, Fractional part IQN, Fractional part IQN x int32, Integer part IQN, Integer part IQN x int32, IQN to Float, IQN x int32, IQN x IQN, IQN1 to IQN2, IQN1 x IQN2, Magnitude IQN, Saturate IQN, Square Root IQN, Trig Fcn IQN

### **Purpose**

Four-quadrant arc tangent

# Library

tiigmathlib in Embedded Target for TI C2000 DSP

## **Description**

This block computes the four-quadrant arc tangent of the IQ number inputs and produces IQ number output.

**Note** The implementation of this block does not call the corresponding Texas Instruments library function during code generation. The TI function uses a global Q setting and the MathWorks code used by this block dynamically adjusts the Q format based on the block input. See "About the IQmath Library" on page 2-2 for more information.

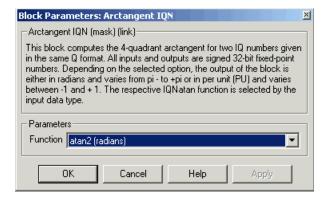

## Dialog Box

#### **Function**

Type of arc tangent to calculate, either

- atan2 Compute the four-quadrant arc tangent with output in radians with values between -pi and +pi.

- atan2PU Compute the four-quadrant arc tangent per unit. If atan2(B,A) is greater than or equal to zero, atan2PU(B,A) = atan2(B,A)/2\*pi. Otherwise, atan2PU(B,A)

# **Arctangent IQN**

= atan2(B,A)/2\*pi+1. The output is in per-unit radians with values from 0 to 2pi radians.

## **See Also**

Absolute IQN, Division IQN, Float to IQN, Fractional part IQN, Fractional part IQN x int32, Integer part IQN, Integer part IQN x int32, IQN to Float, IQN x int32, IQN x IQN, IQN1 to IQN2, IQN1 x IQN2, Magnitude IQN, Saturate IQN, Square Root IQN, Trig Fcn IQN

## **Purpose**

Analog-to-digital converter (ADC)

# Library

c2400dspchiplib in Embedded Target for TI C2000 DSP

## **Description**

The C24x ADC block configures the C24x ADC to perform analog-to-digital conversion of signals connected to the selected ADC input pins. The ADC block outputs digital values representing the analog input signal and stores the converted values in the result register of your digital signal processor. You use this block to capture and digitize analog signals from external sources such as signal generators, frequency generators, or audio devices.

#### **Triggering**

The C24x ADC trigger mode depends on the internal setting of the Source Start-of-Conversion (SOC) signal. The ADC is usually triggered by software at the sample time intervals specified in the ADC block—this is unsynchronized mode.

In synchronized mode, the Event (EV) Manager associated with the same module as the ADC triggers the ADC. In this case, the ADC is synchronized with the pulse width modulator (PWM) waveforms generated by the same EV unit via the **ADC Start Event** signal setting. The **ADC Start Event** is set in the C24x PWM block. See that block for information on the settings.

**Note** The ADC cannot be synchronized with the PWM if the ADC is in cascaded mode (see below).

### Output

The output of the C24x ADC is a vector of uint16 values. The output values are in the range 0 to 1023 because the C24x ADC is a 10-bit converter.

#### **Modes**

The C24x ADC block supports ADC sequential operation in dual and cascaded modes. In dual mode, either module A or module B can be used for the ADC block, and two ADC blocks are allowed in the model. In cascaded mode, both module A and module B are used for a single ADC block.

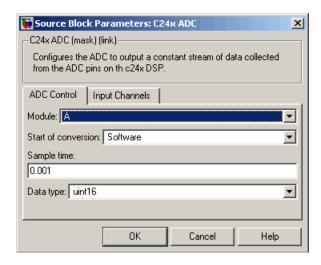

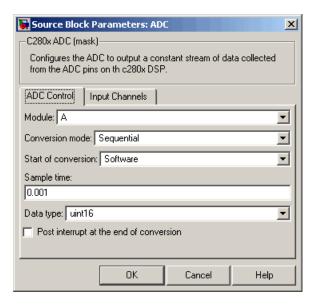

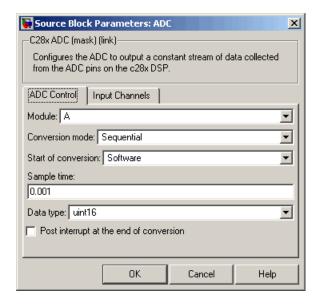

# Dialog Box

#### **ADC Control pane**

#### Module

Specifies which DSP module to use.

- A Enables the ADC channels in module A (ADCINA0 through ADCINA7)

- B Enables the ADC channels in module B (ADCINB0 through ADCINB7)

- A and B Enables the ADC channels in both modules A and B (ADCINA0 through ADCINA7 and ADCINB0 through ADCINB7).

#### Start of conversion

Type of signal that triggers sequential conversions to begin:

- Software Signal from software

- EVA Signal from event manager A

- EVB Signal from event manager B

- External pin— Signal from external hardware

#### Sample time

Time in seconds between consecutive sets of samples that are converted for the selected ADC channel(s). This is the rate at which values are read from the result registers. See "Scheduling and Timing" on page 1-11 for more information on timing.

To set different sample times for different groups of ADC channels, you must add separate C24x ADC blocks to your model and set the desired sample times for each block.

#### Data type

Date type of the output data. Valid data types are auto, double, single, int8, uint8, int16, uint16, int32, or uint32.

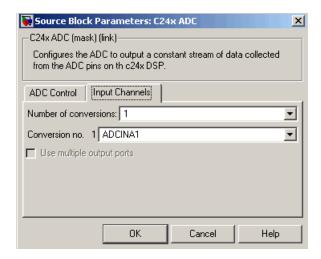

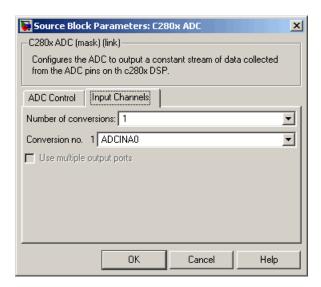

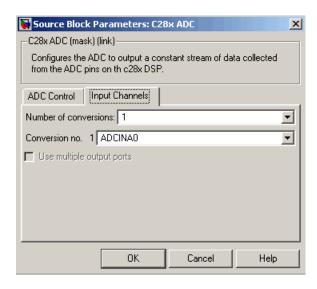

### **Input Channels pane**

#### **Number of conversions**

Number of analog-to-digital conversions to perform in a single sampling sequence.

#### Conversion no.

Specific ADC channel to associate with each conversion number. In simultaneous mode, a pair of ADC channels is associated with each conversion. In oversampling mode, a signal at a given ADC channel can be sampled multiple times during a single conversion sequence. To oversample, specify the same channel for more than one conversion.

#### Use multiple output ports

If more than one ADC channel is used for conversion, you can use separate ports for each output and show the output ports on the block. If you use more than one channel and do not use multiple output ports, the data is output in a single vector.

**Note** The Discrete Filter block in Simulink accepts only mono input. To connect a C24x ADC block to this block, you must output a single channel or connect only one of the ADC's output ports to a Discrete Filter block.

# See Also C24x PWM

# C24x CAN Receive

## **Purpose**

Enhanced Control Area Network receive mailbox

# Library

c2400dspchiplib in Embedded Target for TI C2000 DSP

# **Description**

The C24x Control Area Network (CAN) Receive block generates source code for receiving CAN messages through a CAN mailbox. The CAN module on the DSP chip provides serial communication capability and has six mailboxes — two for receive, two for transmit, and two configurable for receive or transmit. The C24x supports CAN data frames in standard or extended format.

The C24x CAN Receive block has up to two and, optionally, three output ports.

- The first output port is the function call port, and a function call subsystem should be connected to this port. When a new message is received, this subsystem is executed.

- The second output port is the message data port. The received data is output in the form of a vector of elements of the selected data type. (See **Data type** below for information.)

- The third output port is optional and appears only if **Output** message length is selected.

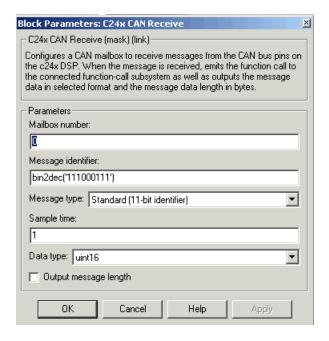

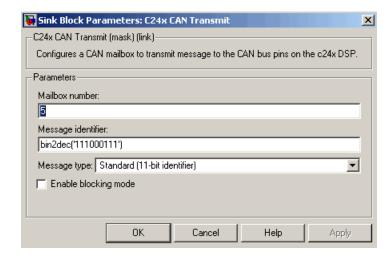

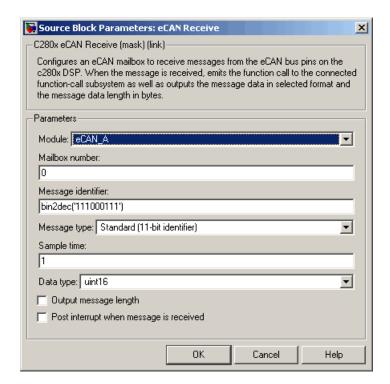

# Dialog Box

#### Mailbox number

Unique number between 0 and 5 that refers to a mailbox area in RAM. Mailboxes 0 and 1 are receive mailboxes, 2 and 3 are configurable for receive or transmit, and 4 and 5 are transmit mailboxes. In standard data frame mode, the mailbox number determines priority.

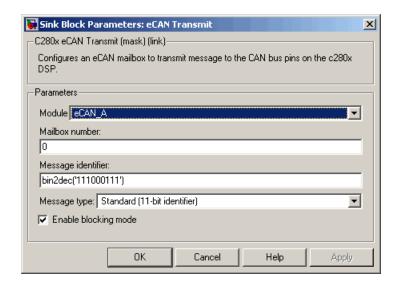

#### Message identifier

Identifier of length 11 bits for standard frame size or length 29 bits for extended frame size in decimal, binary, or hex. If in binary or hex, use bin2dec(' ') or hex2dec(' '), respectively, to convert the entry. The message identifier is associated with a receive mailbox. Only messages that match the mailbox message identifier are accepted into it.

#### Message type

```

Select Standard (11-bit identifier) or Extended (29-bit identifier).

```

#### Sample time

Frequency with which the mailbox is polled to determine if a new message has been received. A new message causes a function call to be emitted from the mailbox.

#### Data type